Validation of Self-Organized Synchronization

Validation of self-organized synchronization in the GHz-regime for the application in future microelectronic systems

VIP+ PLL-Synchronization

The Max-Planck-Institute for the Physics of Complex Systems conducts in collaboration with the Chair for Circuit Design and Network Theory at the Technische Universität Dresden and the Fraunhofer Institute for Reliability and Microintegration IZM a validation project on Self-organized synchronization of mutually delay-coupled electronic clocks.

In the context of the VIP+ validation project “PLL-synchronisation” we develop a modular and scalable architecture design for the implementation of a novel synchronization layer for large, or spatially distributed electronic systems. It relies on self-organized synchronization of mutually coupled electronic clocks. The project plan includes two prototype production runs in BiCMOS technology and the setup of a demonstrator. In networks with up to 288 clocks we will validate that there is no phase-drift between the clocks in the network once a synchronized state has self-organized, and that the quality of such synchronized states exceeds that of an individual clock.

This project will lay the foundation for the application of this novel approach in the next-generation electronic systems, e.g., in communications, antenna arrays, indoor navigation, drone and robot swarms and data-centers.

Download our latest teaser.

The model

We use a phase oscillator model to analyze the dynamics and properties of self-organized synchronized states in networks of mutually delay-coupled electronic clocks. This model has been developed in collaboration with the Vodafone Chair Mobile Communications at the TU-Dresden within the Center for Advancing Electronics Dresden. Experimental results obtained from prototype setups have shown that the model can reliably predict the dynamics of such systems.

PloS one 12 (2), e0171590

European Patent 2957982, filed 20.06.2014 and issued 09.08.2017

New Journal of Physics 16 (11), 113009

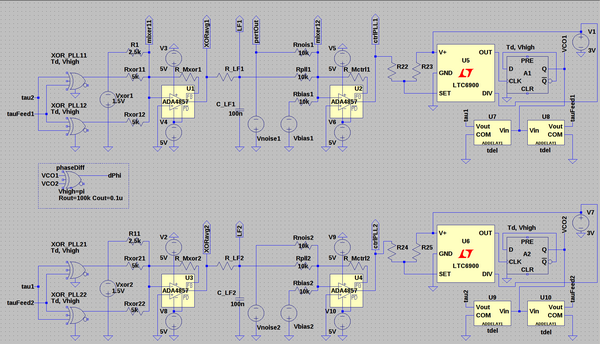

LTspice simulations

In addition to the mathematical modelling we perform LTspice circuit-level simulations of mutually delay-coupled phase-locked loops (PLLs). In this framework we also develop and test novel architecture designs for the PLL nodes and the network. Currently we are setting up the next prototype setup with DPLLs operating in the MHz regime. Testing and simulating components of the system like the tunable delay-lines, the dividers and the signal mixing elements using LTspice libraries of readily available circuitry helps to identify potential problems early on.

Boot-strategies, control and calibration

In order to enable solutions based on self-organized dynamics for technical applications, the behavior of the system must be under control. This is a challenging task for networks of mutually delay-coupled electronic clocks and requires us to provide solutions to different problems.

- When all clocks of such a network are turned on simultaneously, the system can go into different operational states depending on the initial states of the individual clocks. Especially for large systems there exists such a large number of possible states that it is not likely to fall into the desired state of operation. Here we will rely on boot strategies that start-up the network in such ways, that by the end of the booting procedure the system will operate in the desired regime. The most simple strategy to do that is to start out with two mutually coupled clocks to form a core-network and then add the other clocks sequentially to that core.

- The notion of control of self-organization may seem to be contradictory. However, control of self-organized dynamics may be achieved by controlling the system parameters that determine the dynamics. This can only be achieved if said parameters are available to control and a theoretical framework that can predict the systems' self-organized dynamics is available. So far our abstract phase-model approach has proven very successful in predicting the behavior of such clock networks.

- In electrical engineering there is the notion of so called pvt-variations, i.e., process, voltage and temperature variations. While the voltage and temperature variations are dynamic and can change the system parameters on time-scales relevant to the operation and function, the variations introduced by the (production) process are static and may be countered by the calibration of specific components.

Adding a reference clock to self-organized synchronous states

We also aim at combining the strengths of both synchronization concepts, i.e., of hierarchical reference-clock solutions and the self-organized approach with flat hierarchies. This can be achieved by feeding the signal of a high quality reference-clock into a network of mutually delay-coupled clocks. Thereby, the self-organized synchronous state that prevents the phases of the clocks to drift with respect to each other may benefit of the reference clocks' frequency stability. This would connect the synchronous state that has formed over the clock network with external time-references and standards, e.g., TAI and UTC.